Silicon Storage Technology, Inc.

# **Programming User's Manual**

Remote Controller SST65P542R

# **TABLE OF CONTENTS**

| 1.0 | INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 4                                                                 |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| 2.0 | BLOCK DIAGRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                | . 5                                                                 |

| 3.0 | PIN ASSIGNMENTS                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 6                                                                 |

| 4.0 | MEMORY ORGANIZATION                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 7                                                                 |

| 5.0 | MCU CORE AND INSTRUCTION SET                                                                                                                                                                                                                                                                                                                                                                                                                                                 | . 8                                                                 |

|     | 5.1 Registers and Control Bit Assignments 5.1.1 Accumulator (A) 5.1.2 Index Register (X) 5.1.3 Program Counter (PC) 5.1.4 Stack Pointer (SP) 5.1.5 Processor Status Word (PSW) 5.2 Addressing Modes 5.2.1 Inherent (INH). 5.2.2 Immediate (IMM) 5.2.3 Direct (DIR) 5.2.4 Extended (EXT) 5.2.5 Indexed, No Offset (IX). 5.2.6 Indexed, 8-bit Offset (IX1) 5.2.7 Indexed, 16-bit Offset (IX2) 5.2.8 Relative (REL) 5.2.9 Bit Set/Clear (BSC) 5.2.10 Bit test and branch (BTB). | . 9<br>. 9<br>. 9<br>. 10<br>10<br>10<br>11<br>11<br>11<br>12<br>12 |

| 6.0 | I/O REGISTERS DEFINITION                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19                                                                  |

| 7.0 | INTERRUPTS                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 22                                                                  |

| 8.0 | RESETS AND CLOCKS                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 23                                                                  |

| 9.0 | POWER-DOWN MODES                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                     |

|     | 9.1 STOP Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                     |

4/03

| 10.0 | THE CORE TIMER                                                          | . 25 |

|------|-------------------------------------------------------------------------|------|

|      | 10.1 Computer Operating Properly Watchdog Timer Control Register (CWTC) | . 26 |

|      | 10.2 Timer Control and Status Register (TCSR)                           | . 26 |

|      | 10.2.1 Core Timer Overflow (CTOF)                                       | . 26 |

|      | 10.2.2 Real-Time Interrupt Flag (RTIF)                                  | . 26 |

|      | 10.2.3 Timer Overflow Enable (TOFE)                                     | . 26 |

|      | 10.2.4 Real-Time Interrupt Enable (RTIE)                                | . 26 |

|      | 10.2.5 Timer Overflow Flag Clear (TOFC)                                 |      |

|      | 10.2.6 Real-Time Interrupt Flag Clear (RTFC)                            |      |

|      | 10.2.7 Real-Time Interrupt Rate Select (RT1-RT0)                        | . 27 |

|      | 10.3 Core Timer Counter Register (CTCR)                                 | . 27 |

|      | 10.4 COP Watchdog Timer (CWT) Reset                                     | . 27 |

|      | 10.5 Timer During IDLE Mode                                             | . 27 |

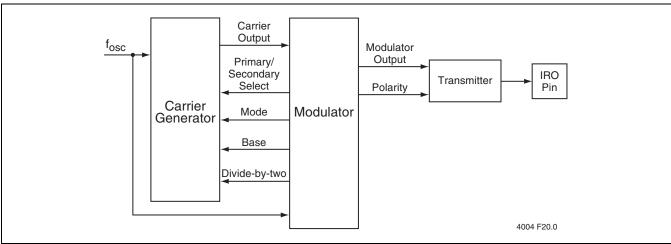

| 11.0 | CARRIER MODULATOR TRANSMITTER (CMT)                                     | . 28 |

|      | 11.1 Carrier Generator                                                  | . 28 |

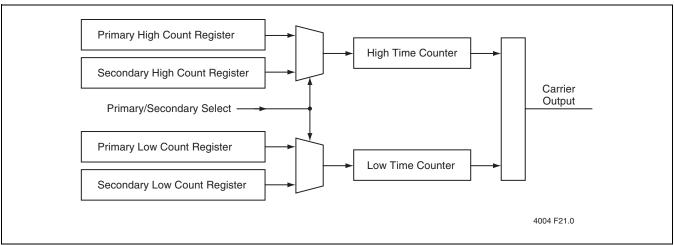

|      | 11.1.1 Time Counter                                                     | . 29 |

|      | 11.1.2 Carrier Generator Data Registers (CHR1, CLR1, CHR2, and CLR2)    | . 30 |

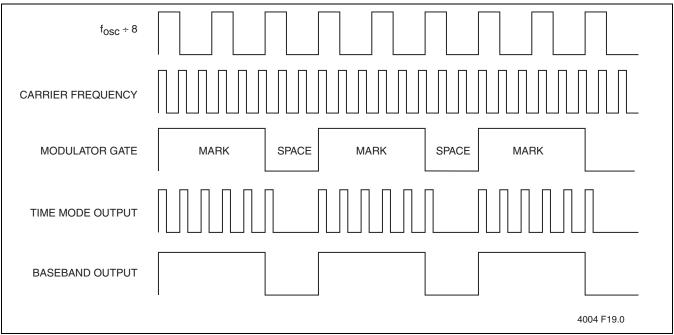

|      | 11.2 Modulator                                                          | . 31 |

|      | 11.2.1 Time mode                                                        | . 31 |

|      | 11.2.2 FSK Mode                                                         |      |

|      | 11.2.3 Extended Space Operation                                         | . 33 |

|      | 11.2.4 End Of Cycle (EOC) Interrupt                                     |      |

|      | 11.2.5 Modulator Period Data Register (MDR1, MDR2, and MDR3)            | . 35 |

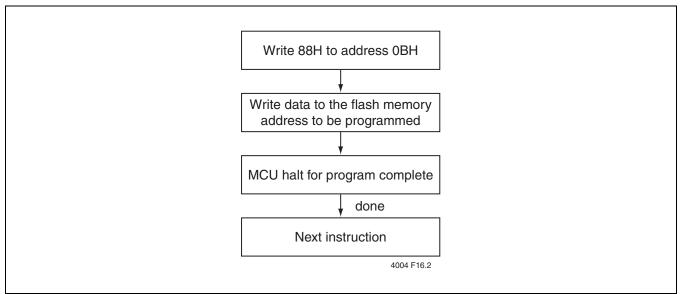

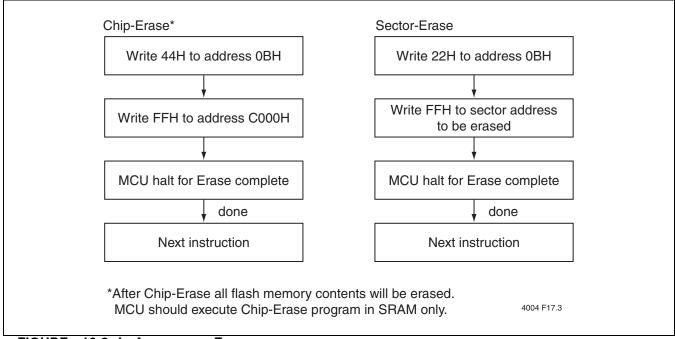

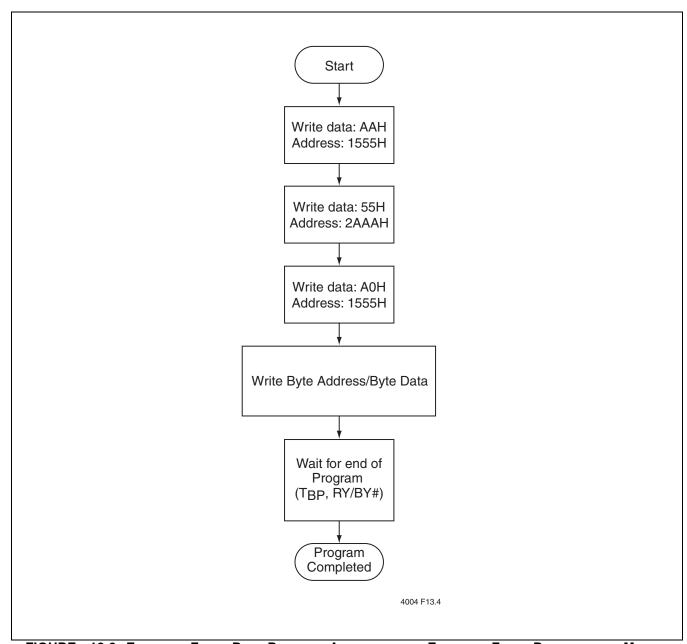

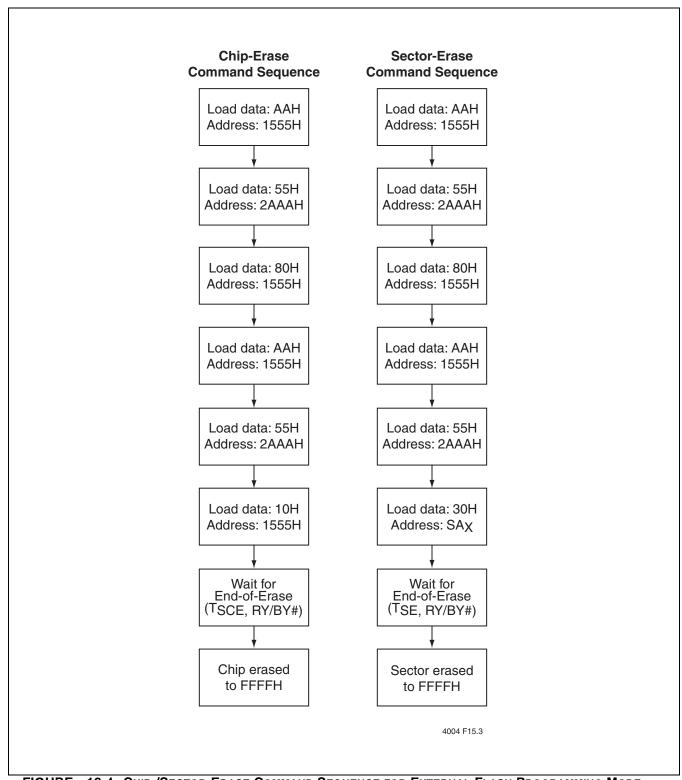

| 12.0 | PROGRAMMING FLOW DIAGRAM                                                | . 36 |

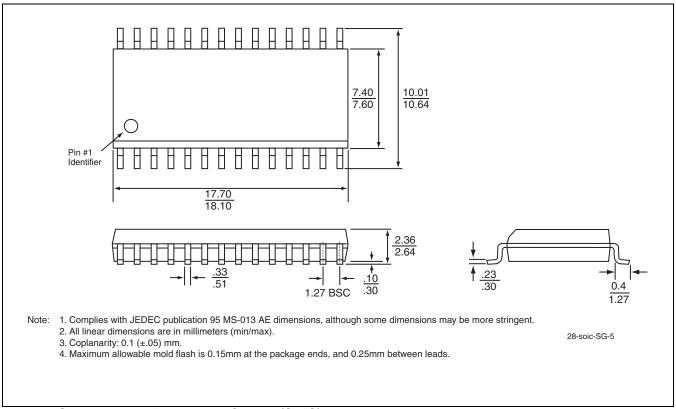

| 13 N | PACKAGING DIAGRAMS                                                      | 30   |

#### 1.0 INTRODUCTION

The SST65P542R is a member of SST's 8-bit, application-specific microcontroller family targeting IR remote controller applications.

The SST65P542R microcontroller provides high-functionality to infrared remote controller products. The device offers flexibility to store different remote control configurations for controlling multiple appliances. The configurations are either programmed at the factory during the manufacturing process or updated through a web download procedure using the serial interface.

Using the SuperFlash nonvolatile memory technology, the SST65P542R enhances the functionality of the conventional universal remote controller devices by integrating multiple functions of a remote controller system in a single chip solution. The built-in LED I/O ports can directly drive LED indicators. The IR transmitter port drives signals to the infrared transmitter, which, in turn, remotely controls appliances.

The SoftPartition flash memory architecture allows seamless partition of the program code, protocol tables, and user data in the small granularity of 128 Byte sectors. The small sector size and fast Erase/Write time greatly increase the time and power efficiency when altering the contents of the flash memory.

The embedded controller is designed and manufactured using SST's patented and proprietary SuperFlash EEPROM technology.

SST's highly reliable SuperFlash technology provides significant advantages over conventional flash memory technology. These advantages translate into significant overall cost savings and reliability benefits for customers.

#### **PRODUCT FEATURES**

- 8-bit MCU Core

- Enhanced 6502 Microprocessor Megacell

- 4 MHz Typical Oscillator Clock Frequency

- 8 MHz maximum clock frequency

- 16 KByte of user programmable flash memory

- 352 Bytes SRAM

- . IR Input Pin for Learning Mode

- Power-down Modes

- Carrier Modulator Transmitter

- Supports Baseband, Pulse Length Modulator (PLM), and Frequency Shift Keying (FSK)

- Core Timer / Counter

- 14-stage multifunctional ripple counter

- Includes timer overflow, POR, RTI, and CWT

#### General Registers:

- Accumulator (8-bit)

- Index Register (8-bit)

#### · Control registers:

- Program Counter (16-bit)

- Stack Pointer (16-bit / 6 addressable bits)

- Condition code register (8-bit)

#### · Addressing modes supported:

- 1. Immediate 3. Extended 5. Indexed, no offset 7. Indexed, 16-bit offset 9. Bit test and branch

- 2. Direct 4. Relative 6. Indexed, 8-bit offset 8. Bit set/clear 10. Inherent

# · Data types supported:

- 1. Bit data (manipulation instructions)

- 2. Byte data

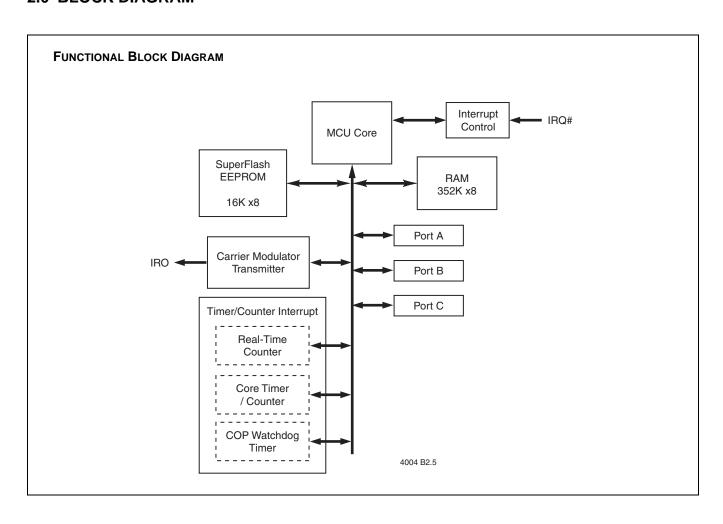

# 2.0 BLOCK DIAGRAM

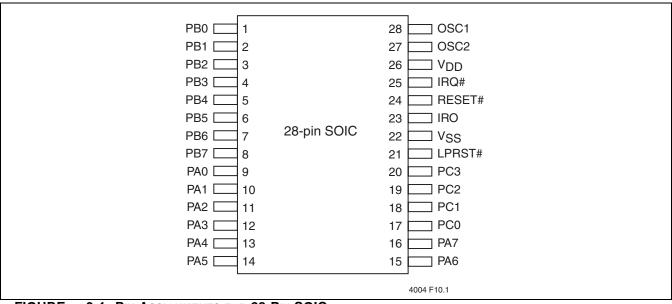

# 3.0 PIN ASSIGNMENTS

FIGURE 3-1: PIN ASSIGNMENTS FOR 28-PIN SOIC

TABLE 3-1: PIN DESCRIPTIONS

| Pins  | Symbol          | Type <sup>1</sup>          | Name and Functions                                                                                                                                                                                                                                                                                  |

|-------|-----------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16-9  | PA[7:0]         | I/O <sup>1</sup>           | <b>Port A:</b> The state of any pin in Port A is software programmable and every line is configured as an input during any external reset.                                                                                                                                                          |

| 8-1   | PB[7:0]         | I/O with internal pull-ups | <b>Port B:</b> The state of any pin in Port B is software programmable and every line is configured as an input during any external reset. Each I/O line contains a programmable interrupt/pull-up for keyscan. PB[7] is used as a serial interface data line when the serial interface is enabled. |

| 20-17 | PC[3:0]         | I/O                        | <b>Port C:</b> Every pin in Port C is a high-current pin and its state is software programmable. All lines are configured as inputs during any external reset.                                                                                                                                      |

| 23    | IRO             | 0                          | <b>IRO:</b> Suitable for driving IR LED biasing logic, the IRO pin is the high-current source and sink output of the carrier modulator transmitter subsystem. Default state is low after any external reset.                                                                                        |

| 21    | LPRST#          | I                          | <b>Low-Power Reset:</b> An active-low pin, LPRST# function sets MCU to low-power reset mode. The MCU, once in low-power reset mode, is held in reset with all processor clocks and crystal oscillator halted. An internal Schmitt trigger is included in the LPRST# pin to improve noise immunity.  |

| 24    | RESET#          | I                          | <b>Reset:</b> By setting the RESET# pin low the MCU is reset to a default state. An internal Schmitt trigger is included in the RESET# pin to improve noise immunity.                                                                                                                               |

| 28    | OSC1            | I                          | Oscillator 1,2: These 2 pins interface with external oscillator circuits.                                                                                                                                                                                                                           |

| 27    | OSC2            | 0                          | A crystal resonator, a ceramic resonator, or an external clock signal can be used.                                                                                                                                                                                                                  |

| 25    | IRQ#            | I                          | <b>Interrupt Request:</b> The IRQ# is negative edge-sensitive triggered. An internal Schmitt trigger is included in the IRQ# pin to improve noise immunity.                                                                                                                                         |

| 26    | $V_{DD}$        | Ī                          | Power Supply: Supply Voltage                                                                                                                                                                                                                                                                        |

| 22    | V <sub>SS</sub> | ı                          | Ground: Circuit ground. (0V reference)                                                                                                                                                                                                                                                              |

T3-1.5 4004

<sup>1.</sup> I = Input O = Output

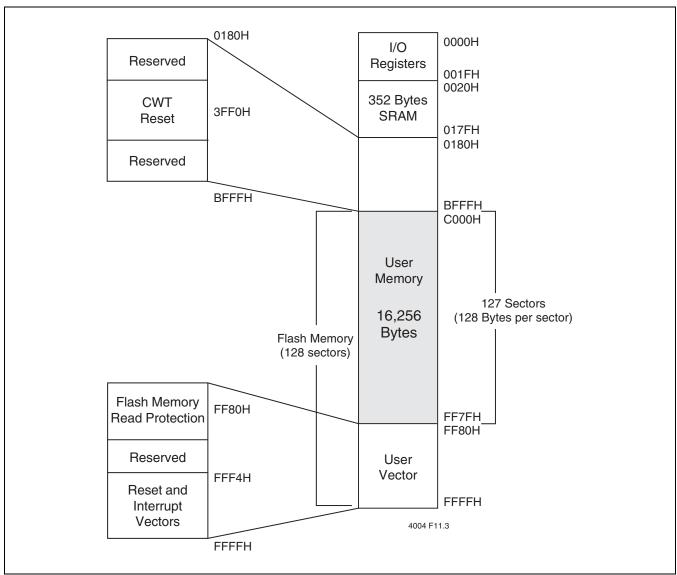

# 4.0 MEMORY ORGANIZATION

The SST65P542R has a total of 64 KByte of addressable memory. A memory map is shown in Figure 4-1. The memory consists of 32 Bytes of I/O registers, 352 Bytes of SRAM, 16 KByte of user flash memory, and 128 Bytes of user vectors.

FIGURE 4-1: MEMORY MAP

# 5.0 MCU CORE AND INSTRUCTION SET

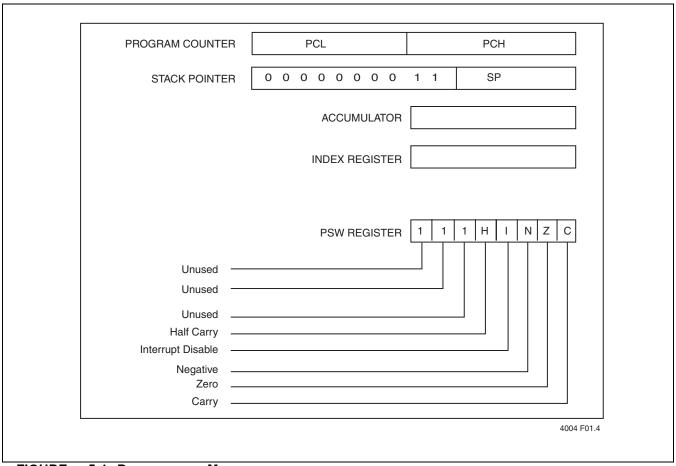

This section provides a description of the MCU core registers, the instruction set and the addressing modes.

# 5.1 Registers and Control Bit Assignments

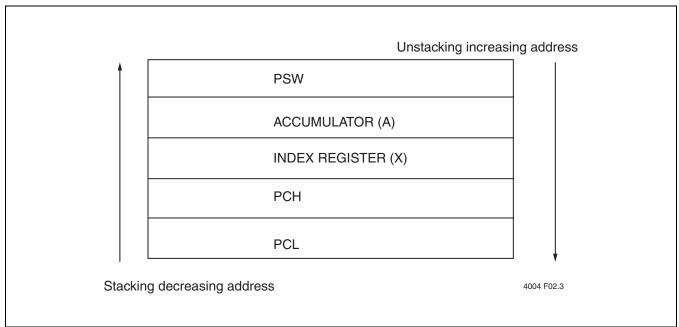

The MCU contains five registers, as shown in the programming model of Figure 5-1. The interrupt stacking order is shown in Figure 5-2.

FIGURE 5-1: PROGRAMMING MODEL

FIGURE 5-2: STACKING ORDER

Stacking decreases memory address and unstacking (Return) increases memory address.

# 5.1.1 Accumulator (A)

The accumulator is a general purpose 8-bit register used to hold operands and results of an arithmetic calculation or data manipulations.

#### 5.1.2 Index Register (X)

The index register is an 8-bit register, which can contain the indexed addressing value used to create an effective address. The index register may also be used as a temporary storage area.

#### 5.1.3 Program Counter (PC)

The program counter is a 16-bit register, which contains the address of the next byte to be fetched.

# 5.1.4 Stack Pointer (SP)

The stack pointer is a 16-bit register, which contains the address of the next free location on the stack. During an MCU reset or the reset stack pointer (RSP) instruction, the stack pointer is set to location 00FFH. The stack pointer is then decremented as data is pushed onto the stack and incremented as data is pulled from the stack. When accessing memory, the 8 most significant bits are permanently set to 00H. These eight bits are appended to the lower 8 significant register bits to produce an address within the range of 00C0H to 00FFH. Subroutines and interrupts may use up to 256 (decimal) locations. If 64 locations are exceeded, i.e. if stack pointer is pointing to 00C0H and stacking operation carried out, the stack pointer wraps around to 00FFH and overwrites the previously stored information. A subroutine call occupies two locations on the stack; an interrupt uses five locations.

# 5.1.5 Processor Status Word (PSW)

The PSW is a 5-bit register. These bits can be individually tested by a program, and specific actions can be taken as a result of their state. Each bit is explained in the following paragraphs.

#### 5.1.5.1 Half Carry (H)

This bit is set during ADD and ADC operations to indicate that a carry has occurred between bits 3 and 4 of the accumulator during an ADD or ADC operation.

#### 5.1.5.2 Interrupt (I)

When this bit is set all maskable interrupts are masked. If an interrupt occurs while this bit is set, the interrupt is latched and remains pending until the interrupt bit is cleared. After any reset, the interrupt mask is set and can be cleared by software instruction (CLI).

#### 5.1.5.3 Negative (N)

When set, this bit indicates that the result of the last arithmetic, logical, or data manipulation was negative.

#### 5.1.5.4 Zero (Z)

When set, this bit indicates that the result of the last arithmetic, logical, or data manipulation was zero.

#### 5.1.5.5 Carry/Borrow (C)

When set, this bit indicates that a carry or borrow out of the arithmetic logical unit (ALU) occurred during the last arithmetic operation. This bit is also affected during bit test and branch instructions and during shifts and rotates.

# 5.2 Addressing Modes

Ten different addressing modes provide programmers with the flexibility to optimize their code for all situations. The various indexed addressing modes make it possible to locate data tables, code conversion tables and scaling tables anywhere in the memory space. Short indexed accesses are single byte instructions; the longest instructions (three bytes) enable access to tables throughout memory. Short absolute (direct) and long absolute (extended) addressing are also included. One or two byte direct addressing instructions access all data bytes in most applications.

Extended addressing permits jump instructions to reach all memory locations. The term 'effective address' (EA) is used in describing the various addressing modes. The effective address is defined as the address from which the argument for an instruction is fetched or stored. The ten addressing modes of the processor are described below. Parentheses are used to indicate 'contents of' the location or register referred to. For example, (PC) indicates the contents of the location pointed to by the PC (program counter). An arrow indicates 'is replaced by' and a colon indicates concatenation of two bytes.

#### 5.2.1 Inherent (INH)

In the inherent addressing mode, all the information necessary to execute the instruction is contained in the opcode. Operations specifying only the index register or accumulator, as well as the control instruction, with no other arguments are included in this mode. These instructions are one byte long.

#### 5.2.2 Immediate (IMM)

In the immediate addressing mode, the operand is contained in the byte immediately following the opcode.

EA = PC+1;  $PC \leftarrow PC+2$

# SST65P542R

# **Programming Reference Manual**

# 5.2.3 Direct (DIR)

In the direct addressing mode, the effective address of the argument is contained in a single byte following the opcode byte. Direct addressing allows the user to directly address the lowest 256 bytes in memory with a single two-byte instruction.

$$EA = (PC+1); PC \leftarrow PC+2$$

Address bus high byte  $\leftarrow$ 0, Address bus low byte  $\leftarrow$ (PC+1)

#### 5.2.4 Extended (EXT)

In the extended addressing mode, the effective address of the argument is contained in the two bytes following the opcode byte. Instructions with extended addressing mode are capable of referencing arguments anywhere in memory with a single three-byte instruction.

$$EA = (PC+1):(PC+2); PC \leftarrow PC+3$$

Address bus high byte  $\leftarrow$ (PC+1); Address bus low byte  $\leftarrow$ (PC+2)

#### 5.2.5 Indexed, No Offset (IX)

In the indexed, no offset addressing mode, the effective address of the argument is contained in the 8-bit index register. This addressing mode can access the first 256 memory locations. These instructions are only one byte long. This mode is often used to move a pointer through a table or to hold the address of a frequently referenced RAM or I/O location.

$$EA = (X); PC \leftarrow PC+1$$

Address bus high byte  $\leftarrow$ 0; Address bus low byte  $\leftarrow$ (X)

#### 5.2.6 Indexed, 8-bit Offset (IX1)

In the indexed, 8-bit offset addressing mode, the effective address is the sum of the contents of the unsigned 8-bit index register and the unsigned byte following the opcode. Therefore the operand can be located anywhere within the lowest 511 memory locations. This addressing mode is useful for selecting the m<sup>th</sup> element in an n element table.

$$EA = (X)+(PC+1)$$

;  $PC \leftarrow PC+2$

Address bus high byte  $\leftarrow$ K; Address bus low byte  $\leftarrow$ (X)+(PC+1)

where K = the carry from the addition of (X) and (PC+1)

#### 5.2.7 Indexed, 16-bit Offset (IX2)

In the indexed, 16-bit offset addressing mode, the effective address is the sum of the contents of the unsigned 8-bit index register and the two unsigned bytes following the opcode. This address mode can be used in a manner similar to indexed, 8-bit offset except that this three-byte instruction allows tables to be anywhere in memory. As with direct and extended addressing, the assembler determines the shortest form of indexed addressing.

$$EA = (X)+[(PC+1):(PC+2)]; PC \leftarrow PC+3$$

Address bus high byte  $\leftarrow$ (PC+1)+K; Address bus low byte  $\leftarrow$ (X)+(PC+2)

where K = the carry from the addition of (X) and (PC+2)

# 5.2.8 Relative (REL)

The relative addressing mode is only used in branch instructions. In relative addressing, the contents of the 8-bit signed byte (the offset) following the opcode is sign-extended and added to the PC if, and only if, the branch conditions are true. Otherwise, control proceeds to the next instruction. The span of relative addressing is from -126 to +129 from the opcode address. The programmer need not calculate the offset when using the assembler, since it calculates the proper offset and checks to see that it is within the span of the branch.

EA = PC+2+(PC+1); PC

$$\leftarrow$$

EA if branch taken; otherwise PC  $\leftarrow$ PC+2

## 5.2.9 Bit Set/Clear (BSC)

In the bit set/clear addressing mode, the bit to be set or cleared is part of the opcode. The byte following the opcode specifies the address of the byte in which the specified bit is to be set or cleared. Any read/write bit in the first 256 locations of memory can be selectively set or cleared with a single two-byte instruction.

$$EA = (PC+1); PC \leftarrow PC+2$$

Address bus high byte  $\leftarrow$ 0; Address bus low byte  $\leftarrow$ (PC+1)

## 5.2.10 Bit test and branch (BTB)

The bit test and branch addressing mode is a combination of direct addressing and relative addressing mode. The bit to be tested and its condition (set or clear) is included in the opcode. The address of the byte to be tested is in the single byte immediately following the opcode byte (EA1). The signed relative 8-bit offset in the third byte is sign-extended and added to the PC if the specified bit is set or cleared in the specified memory location. This single three-byte instruction allows the program to branch based on the condition of any readable bit in the first 256 locations of memory. The span of branch is from -125 to +130 from the opcode address. The state of the tested bit is also transferred to the carry bit of the condition code register.

EA1 = (PC+1); PC

$$\leftarrow$$

PC+2

Address bus high byte  $\rightarrow$ 0; Address bus low byte  $\rightarrow$ (PC+1)

EA2 = PC+3+(PC+2); PC  $\leftarrow$ EA2 if branch taken;

otherwise PC  $\leftarrow$ PC+3

# 5.3 Instruction Set

Table 5-1 summarizes the MCU instruction set. A description of the instructions and an explanation of abbreviations follows the table on page 18.

TABLE 5-1: MCU INSTRUCTION TABLE (1 of 5)

| Mnemonic | Explanation                                                                      | Address<br>Mode (n) | Hex<br>Opcode | Number of<br>Machine Cycles | Number of<br>Bytes | Flags<br>Affected |

|----------|----------------------------------------------------------------------------------|---------------------|---------------|-----------------------------|--------------------|-------------------|

| ADC      | Add memory to accumulator                                                        | IMM                 | A9            | 2                           | 2                  | H-NZC             |

|          | with carry A+M+C →A                                                              | DIR                 | В9            | 3                           | 2                  |                   |

|          |                                                                                  | EXT                 | C9            | 4                           | 3                  |                   |

|          |                                                                                  | IX                  | F9            | 3                           | 1                  |                   |

|          |                                                                                  | IX1                 | E9            | 4                           | 2                  |                   |

|          |                                                                                  | IX2                 | D9            | 5                           | 3                  |                   |

| ADD      | Add memory to accumulator                                                        | IMM                 | AB            | 2                           | 2                  | H-NZC             |

|          | A+M →A                                                                           | DIR                 | BB            | 3                           | 2                  |                   |

|          |                                                                                  | EXT                 | СВ            | 4                           | 3                  |                   |

|          |                                                                                  | IX                  | FB            | 3                           | 1                  |                   |

|          |                                                                                  | IX1                 | EB            | 4                           | 2                  |                   |

|          |                                                                                  | IX2                 | DB            | 5                           | 3                  |                   |

| AND      | "AND" memory with                                                                | IMM                 | A4            | 2                           | 2                  | N Z -             |

|          | accumulator                                                                      | DIR                 | B4            | 3                           | 2                  |                   |

|          | A&M →A                                                                           | EXT                 | C4            | 4                           | 3                  |                   |

|          |                                                                                  | IX                  | F4            | 3                           | 1                  |                   |

|          |                                                                                  | IX1                 | E4            | 4                           | 2                  |                   |

|          |                                                                                  | IX2                 | D4            | 5                           | 3                  |                   |

| ASR      | Shift right one bit                                                              | INH (A)             | 47            | 3                           | 1                  | NZC               |

|          | (accumulator or memory)                                                          | INH (X)             | 57            | 3                           | 1                  |                   |

|          | b0 →C                                                                            | DIR                 | 37            | 5                           | 2                  |                   |

|          | b7 held constant                                                                 | IX                  | 77            | 5                           | 1                  |                   |

|          |                                                                                  | IX1                 | 67            | 6                           | 2                  |                   |

| ASL      | (same as LSL)                                                                    | INH (A)             | 48            | 3                           | 1                  | NZC               |

|          | Shift left one bit                                                               | INH (X)             | 58            | 3                           | 1                  |                   |

|          | (accumulator or memory)                                                          | DIR                 | 38            | 5                           | 2                  |                   |

|          | b7 <i>→</i> C                                                                    | IX                  | 78            | 5                           | 1                  |                   |

|          | 0 →b0                                                                            | IX1                 | 68            | 6                           | 2                  |                   |

| BCC      | Branch on carry clear<br>Branch on C = 0                                         | REL                 | 24            | 3                           | 2                  |                   |

| BCLR     | Clear bit n                                                                      | BSC                 | 11 + 2n       | 5                           | 2                  |                   |

| BCS      | Branch on carry set Branch on C = 1                                              | REL                 | 25            | 3                           | 2                  |                   |

| BEQ      | Branch on result zero Branch on Z = 1                                            | REL                 | 27            | 3                           | 2                  |                   |

| внсс     | Branch if half carry clear<br>Branch on H = 0                                    | REL                 | 28            | 3                           | 2                  |                   |

| BHCS     | Branch if half carry set<br>Branch on H = 1                                      | REL                 | 29            | 3                           | 2                  |                   |

| ВНІ      | Branch if higher<br>Branch if accumulator<br>is higher than memory<br>(unsigned) | REL                 | 22            | 3                           | 2                  |                   |

TABLE 5-1: MCU INSTRUCTION TABLE (CONTINUED) (2 OF 5)

| Mnemonic | Explanation                                                                  | Address<br>Mode (n) | Hex<br>Opcode | Number of<br>Machine Cycles | Number of<br>Bytes | Flags<br>Affected |

|----------|------------------------------------------------------------------------------|---------------------|---------------|-----------------------------|--------------------|-------------------|

| BHS      | Branch if higher or same                                                     | REL                 | 24            | 3                           | 2                  |                   |

|          | Branch if accumulator                                                        |                     |               |                             |                    |                   |

|          | is higher or same                                                            |                     |               |                             |                    |                   |

|          | as memory (C = 0)                                                            |                     |               |                             |                    |                   |

| BIH      | Branch if interrupt line is high                                             | REL                 | 2F            | 3                           | 2                  |                   |

| BIL      | Branch if interrupt line is low                                              | REL                 | 2E            | 3                           | 2                  |                   |

| BIT      | Tests bits in memory: A^M                                                    | IMM                 | A5            | 2                           | 2                  | NZ-               |

|          | (logical compare)                                                            | DIR                 | B5            | 3                           | 2                  |                   |

|          |                                                                              | EXT                 | C5            | 4                           | 3                  |                   |

|          |                                                                              | IX                  | F5            | 3                           | 1                  |                   |

|          |                                                                              | IX1<br>IX2          | E5<br>D5      | 4<br>5                      | 2 3                |                   |

| DI O     | Due a de if levre                                                            |                     |               |                             |                    |                   |

| BLO      | Branch if lower Branch if accumulator is lower Branch on                     | REL                 | 25            | 3                           | 2                  |                   |

| BLS      | Branch if low or same Branch if accumulator is lower than or equal to memory | REL                 | 23            | 3                           | 2                  |                   |

| BMC      | Branch if interrupt                                                          | REL                 | 2C            | 3                           | 2                  |                   |

| DIVIO    | mask bit is clear                                                            | I I I               | 20            |                             | _                  |                   |

| BMI      | Branch if minus branch on N = 1                                              | REL                 | 2B            | 3                           | 2                  |                   |

| BMS      | Branch if interrupt<br>mask bit is set<br>Branch on I = 1                    | REL                 | 2D            | 3                           | 2                  |                   |

| BNE      | Branch if not equal Branch on Z = 0                                          | REL                 | 26            | 3                           | 2                  |                   |

| BPL      | Branch if plus<br>Branch on N = 0                                            | REL                 | 2A            | 3                           | 2                  |                   |

| BRA      | Branch always                                                                | REL                 | 20            | 3                           | 2                  |                   |

| BRN      | Branch never                                                                 | REL                 | 21            | 3                           | 2                  |                   |

| BRCLR    | Branch if bit n is clear                                                     | ВТВ                 | 1 + 2n        | 5                           | 3                  | C                 |

| BRSET    | Branch if bit n is set                                                       | ВТВ                 | 2n            | 5                           | 3                  | C                 |

| BSET     | Set bit n                                                                    | BSC                 | 10 + 2n       | 5                           | 2                  |                   |

| BSR      | Branch to subroutine                                                         | REL                 | AD            | 6                           | 2                  |                   |

| CLC      | Clear carry flag 0 →C                                                        | INH                 | 98            | 2                           | 1                  | 0                 |

| CLI      | Clear interrupt mask bit 0 →I                                                | INH                 | 9A            | 2                           | 1                  | -0                |

| CLR      | Clear                                                                        | INH (A)             | 4F            | 3                           | 1                  | 01-               |

|          |                                                                              | INH (X)             | 5F            | 3                           | 1                  |                   |

|          |                                                                              | DIR                 | 3F            | 5                           | 2                  |                   |

|          |                                                                              | IX                  | 7F            | 5                           | 1                  |                   |

|          |                                                                              | IX1                 | 6F            | 6                           | 2                  |                   |

TABLE 5-1: MCU INSTRUCTION TABLE (CONTINUED) (3 OF 5)

| Mnemonic | Explanation                | Address<br>Mode (n) | Hex<br>Opcode | Number of<br>Machine Cycles | Number of<br>Bytes | Flags<br>Affected |

|----------|----------------------------|---------------------|---------------|-----------------------------|--------------------|-------------------|

| CMP      | Arithmetic compare         | IMM                 | A1            | 2                           | 2                  | NZC               |

|          | memory and accumulator     | DIR                 | B1            | 3                           | 2                  |                   |

|          | (unsigned)                 | EXT                 | C1            | 4                           | 3                  |                   |

|          | A - M                      | IX                  | F1            | 3                           | 1                  |                   |

|          |                            | IX1                 | E1            | 4                           | 2                  |                   |

|          |                            | IX2                 | D1            | 5                           | 3                  |                   |

| COM      | Component                  | INH (A)             | 43            | 3                           | 1                  | N Z 1             |

|          | (one's complement)         | INH (X)             | 53            | 3                           | 1                  |                   |

|          |                            | DIR                 | 33            | 5                           | 2                  |                   |

|          |                            | IX                  | 73            | 5                           | 1                  |                   |

|          |                            | IX1                 | 63            | 6                           | 2                  |                   |

| CPX      | Arithmetic compare         | IMM                 | A3            | 2                           | 2                  | NZC               |

|          | memory and index X         | DIR                 | В3            | 3                           | 2                  |                   |

|          | (unsigned)                 | EXT                 | C3            | 4                           | 3                  |                   |

|          | X-M                        | IX                  | F3            | 3                           | 1                  |                   |

|          |                            | IX1                 | E3            | 4                           | 2                  |                   |

|          |                            | IX2                 | D3            | 5                           | 3                  |                   |

| DEC      | Decrement by one           | INH (A)             | 4A            | 3                           | 1                  | N Z -             |

|          |                            | INH (X)             | 5A            | 3                           | 1                  |                   |

|          |                            | DIR                 | 3A            | 5                           | 2                  |                   |

|          |                            | IX                  | 7A            | 5                           | 1                  |                   |

|          |                            | IX1                 | 6A            | 6                           | 2                  |                   |

| EOR      | "Exclusive or" memory      | IMM                 | A8            | 2                           | 2                  | N Z -             |

|          | with accumulator           | DIR                 | B8            | 3                           | 2                  |                   |

|          | $A \wedge M \rightarrow A$ | EXT                 | C8            | 4                           | 3                  |                   |

|          |                            | IX                  | F8            | 3                           | 1                  |                   |

|          |                            | IX1                 | E8            | 4                           | 2                  |                   |

|          |                            | IX2                 | D8            | 5                           | 3                  |                   |

| INC      | Increment by one           | INH (A)             | 4C            | 3                           | 1                  | N Z -             |

|          |                            | INH (X)             | 5C            | 3                           | 1                  |                   |

|          |                            | DIR                 | 3C            | 5                           | 2                  |                   |

|          |                            | IX                  | 7C            | 5                           | 1                  |                   |

|          |                            | IX1                 | 6C            | 6                           | 2                  |                   |

| JMP      | Jump to new location       | DIR                 | BC            | 2                           | 2                  |                   |

|          | (PC + 1) →PCL              | EXT                 | CC            | 3                           | 3                  |                   |

|          | (PC + 2) →PCH              | IX                  | FC            | 2                           | 1                  |                   |

|          |                            | IX1                 | EC            | 3                           | 2                  |                   |

|          |                            | IX2                 | DC            | 4                           | 3                  |                   |

| JSR      | Jump to new location       | DIR                 | BD            | 5                           | 2                  |                   |

|          | saving return address      | EXT                 | CD            | 6                           | 3                  |                   |

|          | PC + 2↓                    | IX                  | FD            | 5                           | 1                  |                   |

|          | (PC + 1) →PCL              | IX1                 | ED            | 6                           | 2                  |                   |

|          | (PC + 2) →PCH              | IX2                 | DD            | 7                           | 3                  |                   |

TABLE 5-1: MCU INSTRUCTION TABLE (CONTINUED) (4 OF 5)

| Mnemonic | Explanation                             | Address<br>Mode (n) | Hex<br>Opcode | Number of<br>Machine Cycles | Number of<br>Bytes | Flags<br>Affected |

|----------|-----------------------------------------|---------------------|---------------|-----------------------------|--------------------|-------------------|

| LDA      | Load accumulator                        | IMM                 | A6            | 2                           | 2                  | N Z -             |

|          | with memory                             | DIR                 | B6            | 3                           | 2                  |                   |

|          | $M \rightarrow A$                       | EXT                 | C6            | 4                           | 3                  |                   |

|          |                                         | IX                  | F6            | 3                           | 1                  |                   |

|          |                                         | IX1                 | E6            | 4                           | 2                  |                   |

|          |                                         | IX2                 | D6            | 5                           | 3                  |                   |

| LDX      | Load index X with memory                | IMM                 | AE            | 2                           | 2                  | N Z -             |

|          | $M \rightarrow X$                       | DIR                 | BE            | 3                           | 2                  |                   |

|          |                                         | EXT                 | CE            | 4                           | 3                  |                   |

|          |                                         | IX                  | FE            | 3                           | 1                  |                   |

|          |                                         | IX1                 | EE            | 4                           | 2                  |                   |

|          |                                         | IX2                 | DE            | 5                           | 3                  |                   |

| LSL      | (same as ASL)                           | INH (A)             | 48            | 3                           | 1                  | NZC               |

|          | Shift left one bit                      | INH (X)             | 58            | 3                           | 1                  |                   |

|          | (accumulator or memory)                 | DIR                 | 38            | 5                           | 2                  |                   |

|          | b7 <i>→</i> C                           | IX                  | 78            | 5                           | 1                  |                   |

|          | 0 →b0                                   | IX1                 | 68            | 6                           | 2                  |                   |

| LSR      | Shift right one bit                     | INH (A)             | 44            | 3                           | 1                  | 0ZC               |

|          | (memory or accumulator)                 | INH (X)             | 54            | 3                           | 1                  |                   |

|          | b0 <i>→</i> C                           | DIR                 | 34            | 5                           | 2                  |                   |

|          | 0 <i>→</i> b7                           | IX                  | 74            | 5                           | 1                  |                   |

|          |                                         | IX1                 | 64            | 6                           | 2                  |                   |

| MUL      | Multiplication $X * A \rightarrow X: A$ | INH (A)             | 42            | 11                          | 1                  | 00                |

| NEG      | Negate                                  | INH (A)             | 40            | 3                           | 1                  | NZC               |

|          | (Two's complement)                      | INH (X)             | 50            | 3                           | 1                  |                   |

|          | (                                       | DIR                 | 30            | 5                           | 2                  |                   |

|          |                                         | IX                  | 70            | 5                           | 1                  |                   |

|          |                                         | IX1                 | 60            | 6                           | 2                  |                   |

| NOP      | No operation                            | INH                 | 9D            | 2                           | 1                  |                   |

| ORA      | "OR" memory with                        | IMM                 | AA            | 2                           | 2                  | N Z -             |

| Olut     | accumulator                             | DIR                 | BA            | 3                           | 2                  | 112               |

|          | A   M →A                                | EXT                 | CA            | 4                           | 3                  |                   |

|          | 7.1 7.                                  | IX                  | FA            | 3                           | 1                  |                   |

|          |                                         | IX1                 | EA            | 4                           | 2                  |                   |

|          |                                         | IX2                 | DA            | 5                           | 3                  |                   |

| ROL      | Rotate one bit left                     | INH (A)             | 49            | 3                           | 1                  | NZC               |

| NOL      | through carry (memory                   | INH (X)             | 59            | 3                           | 1                  | 1120              |

|          | or accumulator)                         | DIR                 | 39            | 5                           | 2                  |                   |

|          | or accumulator)                         | IX                  | 79            | 5                           | 1                  |                   |

|          |                                         | IX1                 | 69            | 6                           | 2                  |                   |

| ROR      | Rotate one bit right                    | INH (A)             | 46            | 3                           | 1                  | NZC               |

| NOR      | through carry (memory                   | INH (X)             | 56            | 3                           |                    | NZC               |

|          | or accumulator)                         | DIR                 | 36            | 5                           | 2                  |                   |

|          | or accumulator)                         | IX                  | 76            | 5                           | 1                  |                   |

|          |                                         | IX1                 | 66            | 6                           | 2                  |                   |

| RSP      | Popot stock points:                     |                     | 9C            | 2                           |                    |                   |

|          | Reset stack pointer                     | INH                 |               |                             | 1                  | 00000             |

| RTI      | Return from interrupt PC; P             | INH                 | 80            | 9                           | 1                  | ?????             |

TABLE 5-1: MCU INSTRUCTION TABLE (CONTINUED) (5 of 5)

| Mnemonic | Explanation                                 | Address<br>Mode (n) | Hex<br>Opcode | Number of<br>Machine Cycles | Number of<br>Bytes | Flags<br>Affected |

|----------|---------------------------------------------|---------------------|---------------|-----------------------------|--------------------|-------------------|

| RTS      | Return from subroutine<br>PC ↑ ; PC + 1 →PC | INH                 | 81            | 6                           | 1                  |                   |

| SBC      | Subtract memory                             | IMM                 | A2            | 2                           | 2                  | NZC               |

|          | from accumulator                            | DIR                 | B2            | 3                           | 2                  |                   |

|          | with borrow                                 | EXT                 | C2            | 4                           | 3                  |                   |

|          | A-M-C →A                                    | IX                  | F2            | 3                           | 1                  |                   |

|          |                                             | IX1                 | E2            | 4                           | 2                  |                   |

|          |                                             | IX2                 | D2            | 5                           | 3                  |                   |

| SEC      | Set carry flag<br>1 <i>→</i> C              | INH                 | 99            | 2                           | 1                  | 1                 |

| SEI      | Set interrupt mask bit I →1                 | INH                 | 9B            | 2                           | 1                  | -1                |

| STA      | Store accumulator in memory                 | DIR                 | B7            | 4                           | 2                  | N Z -             |

|          | A →M                                        | EXT                 | C7            | 5                           | 3                  |                   |

|          |                                             | IX                  | F7            | 4                           | 1                  |                   |

|          |                                             | IX1                 | E7            | 5                           | 2                  |                   |

|          |                                             | IX2                 | D7            | 6                           | 3                  |                   |

| STX      | Store index X in memory                     | DIR                 | BF            | 4                           | 2                  | N Z -             |

|          | X →M                                        | EXT                 | CF            | 5                           | 3                  |                   |

|          |                                             | IX                  | FF            | 4                           | 1                  |                   |

|          |                                             | IX1                 | EF            | 5                           | 2                  |                   |

|          |                                             | IX2                 | DF            | 6                           | 3                  |                   |

| SUB      | Subtract memory                             | IMM                 | A0            | 2                           | 2                  | NZC               |

|          |                                             | DIR                 | В0            | 3                           | 2                  |                   |

|          |                                             | EXT                 | C0            | 4                           | 3                  |                   |

|          |                                             | IX                  | F0            | 3                           | 1                  |                   |

|          |                                             | IX1                 | E0            | 4                           | 2                  |                   |

|          |                                             | IX2                 | D0            | 5                           | 3                  |                   |

| SWI      | Software interrupt                          | INH                 | 83            | 10                          | 1                  | -1                |

| TAX      | Transfer accumulator<br>to index X<br>A →X  | INH                 | 97            | 2                           | 1                  |                   |

| TST      | Test for negative or                        | INH (A)             | 4D            | 3                           | 1                  | N Z -             |

|          | zero                                        | INH (X)             | 5D            | 3                           | 1                  |                   |

|          |                                             | DIR                 | 3D            | 4                           | 2                  |                   |

|          |                                             | IX                  | 7D            | 4                           | 1                  |                   |

|          |                                             | IX1                 | 6D            | 5                           | 2                  |                   |

| TXA      | Transfer index X to accumulator X →A        | INH                 | 9F            | 2                           | 1                  |                   |

T5-1.5 4004

#### Description

The following is the description of each instruction and the operation during the execution of each instruction.

The key for MCU instructions is as follows:

The first three letters are the opcode the actual mnemonic of the instruction. The possible addressing modes are indicated by the letters following the opcode and they are as follows:

IMM: immediate addressing

INH (A): inherent addressing with respect to Accumulator INH (X): inherent addressing with respect to Index Register

DIR: direct addressing EXT: extended addressing

IX: indexed addressing (no offset)

IX1: indexed addressing with one byte offset IX2: indexed addressing with two byte offset

BSC: bit set / clear

BTB: bit test and branch REL: relative addressing

The following abbreviations are used besides the ones used for addressing mode:

A accumulator

C carry flag

H half carry flag

I interrupt flag

M memory

N negative flag

PC program counter

PCL program counter lower byte

PCH program counter higher byte

SP stack pointer

X index register

Z zero flag

| OR function

& AND function

^ Exclusive OR function ??? load PSW from stack

- not affected

Machine cycle is two oscillator clock cycles.

# 6.0 I/O REGISTERS DEFINITION

The 32 Bytes of I/O registers occupy address locations from 0000H to 001FH and include general purpose I/O pin registers, on-chip peripheral control registers, and SuperFlash Function Registers.

TABLE 6-1: I/O REGISTER DESCRIPTIONS

| Address  |                                                |

|----------|------------------------------------------------|

| Location | Register Description                           |

| 0000H    | Port A Data Register                           |

| 0001H    | Port B Data Register                           |

| 0002H    | Port C Data Register                           |

| 0003H    | Reserved                                       |

| 0004H    | Port A Data Direction Register                 |

| 0005H    | Port B Data Direction Register                 |

| 0006H    | Port C Data Direction Register                 |

| 0007H    | Reserved                                       |

| 0008H    | Core Timer Control Status Register             |

| 0009H    | Core Timer Counter Register                    |

| 000AH    | Port B Interrupt Control Register              |

| 000BH    | SuperFlash Function Register (SFFR)            |

| 000CH    | Port B Pull-up Control Register                |

| 000DH    | COP Watchdog Timer Control Register (CWTC)     |

| 000EH    | Serial Interface Control Register (SICON_TR)   |

| 000FH    | Serial Interface Control Register (SICON_LSBF) |

| 0010H    | Carrier Generator High Data Register1 (CHR1)   |

| 0011H    | Carrier Generator Low Data Register1 (CLR1)    |

| 0012H    | Carrier Generator High Data Register2 (CHR2)   |

| 0013H    | Carrier Generator Low Data Register2 (CLR2)    |

| 0014H    | Modulator Control and Status Register (MCSR)   |

| 0015H    | Modulator Data Register1 (MDR1)                |

| 0016H    | Modulator Data Register2 (MDR2)                |

| 0017H    | Modulator Data Register3 (MDR3)                |

| 0018H    | Power Save Control Register (PSCR)             |

| 0019H    | Serial Interface Control Register (SICON_SI)   |

| 001AH    | Serial Interface Data Register (SIDAT)         |

| 001BH    | Serial Interface Status Register (SISTA)       |

| 001CH    | Serial Interface Baud-Rate Register (SIBDR)    |

| 001DH    | Serial Interface Control Register (SICON_AP)   |

| 001EH    | Serial Interface Control Register (SICON_ENSI) |

| 001FH    | IR Input Control Register                      |

T6-1.3 4004

TABLE 6-2: BIT DEFINITIONS OF I/O REGISTERS (1 OF 2)

| Addr  | Register Name                                  | Bit7   | Bit6        | Bit5   | Bit4   | Bit3   | Bit2   | Bit1   | Bit0   |

|-------|------------------------------------------------|--------|-------------|--------|--------|--------|--------|--------|--------|

| 0000H | Port A Data Register                           | PA7    | PA6         | PA5    | PA4    | PA3    | PA2    | PA1    | PA0    |

| 0001H | Port B Data Register                           | PB7    | PB6         | PB5    | PB4    | PB3    | PB2    | PB1    | PB0    |

| 0002H | Port C Data Register                           | X      | X           | Χ      | X      | PC3    | PC2    | PC1    | PC0    |

| 0003H | Reserved                                       | Х      | Х           | Х      | Х      | Х      | Х      | Х      | X      |

| 0004H | Port A Data<br>Direction Register              | DDRA7  | DDRA6       | DDRA5  | DDRA4  | DDRA3  | DDRA2  | DDRA1  | DDRA0  |

| 0005H | Port B Data<br>Direction Register              | DDRB7  | DDRB6       | DDRB5  | DDRB4  | DDRB3  | DDRB2  | DDRB1  | DDRB0  |

| 0006H | Port C Data<br>Direction Register              | Х      | Х           | X      | Х      | DDRC3  | DDRC2  | DDRC1  | DDRC0  |

| 0007H | Reserved                                       | Х      | Х           | Х      | Х      | Х      | Х      | Х      | Х      |

| H8000 | Core Timer Control Status Register             | CTOF   | RTIF        | TOFE   | RTIE   | TOFC   | TRFC   | RT1    | RT0    |

| 0009H | Core Timer Counter<br>Register                 | Х      | Х           | Х      | Х      | Х      | Х      | Х      | Х      |

| 000AH | Port B Interrupt<br>Control Register           | INPRB7 | INPRB6      | INPRB5 | INPRB4 | INPRB3 | INPRB2 | INPRB1 | INPRB0 |

| 000BH | SuperFlash<br>Function Register                | PREN   | MEREN       | SEREN  | Х      | PROG   | MERA   | SERA   | Х      |

| 000CH | Port B Pull-up<br>Control Register             | Х      | Х           | Х      | Х      | Х      | Х      | PU1    | PU0    |

| 000DH | CWT Control Register                           | Х      | Х           | Х      | Х      | Х      | Х      | Х      | CWT_EN |

| 000EH | Serial Interface<br>Control Register           | Х      | Х           | Х      | Х      | Х      | Х      | TR     | X      |

| 000FH | Serial Interface<br>Control Register           | Х      | Х           | Х      | Х      | Х      | LSBF   | Х      | Х      |

| 0010H | Carrier Generator High<br>Data Register (CHR1) | IROLN  | CMT-<br>POL | PH5    | PH4    | PH3    | PH2    | PH1    | PH0    |

| 0011H | Carrier Generator Low<br>Data Register (CLR1)  | IROLP  | Х           | PL5    | PL4    | PL3    | PL2    | PL1    | PL0    |

| 0012H | Carrier Generator High Data Register 2(CHR2)   | Х      | Х           | SH5    | SH4    | SH3    | SH2    | SH1    | SH0    |

| 0013H | Carrier Generator Low<br>Data Register 2(CLR2) | Х      | Х           | SL5    | SL4    | SL3    | SL2    | SL1    | SL0    |

| 0014H | Modulator Control and Status Register (MCSR)   | EOC    | DIV2        | EIMSK  | EXSPC  | BASE   | MODE   | EOCIE  | MCGEN  |

| 0015H | Modulator Data<br>Register 1(MDR1)             | MB11   | MB10        | MB9    | MB8    | SB11   | SB10   | SB9    | SB8    |

| 0016H | Modulator Data<br>Register 2(MDR2)             | MB7    | MB6         | MB5    | MB4    | MB3    | MB2    | MB1    | MB0    |

| 0017H | Modulator Data<br>Register 3(MDR3)             | SB7    | SB6         | SB5    | SB4    | SB3    | SB2    | SB1    | SB0    |

| 0018H | Power Saving<br>Control Register (PSCR)        | EN     | Х           | Х      | Х      | Х      | Х      | STOP   | IDL    |

| 0019H | Serial Interface<br>Control Register           | Х      | Х           | Х      | Х      | Х      | Х      | Х      | SI     |

X = Reserved (Recommended to write "0" to reserved bits for future compatibility)

T6-2.5 4004

TABLE 6-2: BIT DEFINITIONS OF I/O REGISTERS (CONTINUED) (2 OF 2)

| Addr  | Register Name                          | Bit7 | Bit6 | Bit5       | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 |

|-------|----------------------------------------|------|------|------------|------|------|------|------|------|

| 001AH | Serial Interface<br>Data Register      | D7   | D6   | D5         | D4   | D3   | D2   | D1   | D0   |

| 001BH | Serial Interface<br>Status Register    | Х    | Х    | <b>S</b> 5 | S4   | S3   | Х    | Х    | Х    |

| 001CH | Serial Interface<br>Baud-Rate Register | Х    | Х    | Х          | Х    | F3   | F2   | F1   | F0   |

| 001DH | Serial Interface<br>Control Register   | Х    | Х    | Х          | Х    | AP   | Х    | Х    | Х    |

| 001EH | Serial Interface<br>Control register   | Х    | Х    | Х          | ENSI | Х    | Х    | Х    | Х    |

| 001FH | IR Input Control<br>Register           | Х    | Х    | Х          | Х    | Х    | Х    | IREN | IRIN |

X = Reserved (Recommended to write "0" to reserved bits for future compatibility)

T6-2.5 4004

Please see Section 10.0 for Core Timer and Section 11.0 for CMT register definitions. All other register definitions are described in detail in the SST65P542R data sheet.

#### 7.0 INTERRUPTS

The MCU has 6 sources of interrupts including reset, a software interrupt and 4 hardware interrupt lines. If more than one interrupt line is active, the one with highest priority will be serviced first. The interrupt priority from high to low is hardware reset, software interrupt, external interrupt, CMT interrupt, Core Timer interrupt, and Serial Interface interrupt. See Table 7-1 for Interrupt Address Vectors.

TABLE 7-1: MCU INTERRUPT ADDRESS VECTORS

| Interrupt        | Address     | Description                                                           |

|------------------|-------------|-----------------------------------------------------------------------|

| Reset            | FFFEH-FFFFH | Restart vector FFFEH higher byte, FFFFH lower byte                    |

| SWI              | FFFCH-FFFDH | Software interrupt vector FFFCH higher byte, FFFDH lower byte         |

| External/Port B  | FFFAH-FFFBH | External/Port B interrupt vector FFFAH higher byte, FFFBH lower byte  |

| CMT              | FFF8H-FFF9H | CMT interrupt vector FFF8H higher byte, FFF9H lower byte              |

| Core Timer       | FFF6H-FFF7H | Core Timer interrupt vector FFF6H higher byte, FFF7H lower byte       |

| Serial Interface | FFF4H-FFF5H | Serial Interface interrupt vector FFF4H higher byte, FFF5H lower byte |

T7-1.3 4004

All four interrupt lines are masked by the interrupt mask bit (I bit of the Process Status Word Register). The software interrupt is generated by SWI instruction similar to that of any hardware instruction except that it is not maskable (the execution of the SWI instruction is independent of the state of the mask bit).

All external interrupt lines are falling edge triggered and interrupts are always checked before fetching the next instruction.

If interrupt is recognized, before the Program counter jumps to one of the address vectors, the Program Counter, Index Register, Accumulator, and the Process Status Word Register are pushed on to the stack (see Figure 5-2).

22

# **Programming Reference Manual**

#### 8.0 RESETS AND CLOCKS

SST65P542R has two sources for external reset: LPRST# and RESET#.

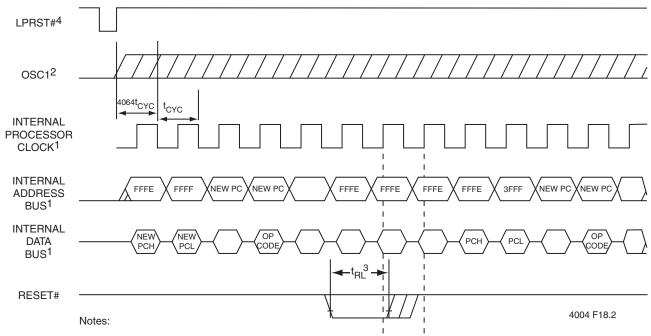

After LPRSET# switches from low to high, 4064 clock cycles are counted before the reset vector address appears on the internal address bus. RESET# immediately resets the MCU without counting the 4064 clock cycles.

Crystal oscillator clock is divided by two to arrive at internal processor and peripheral clock. Figure 8-1 shows RESET# and LPRST# timing diagram.

- Internal timing signal and bus information are not available externally.

Internal Processor Clock is half the frequency of OSC1.

- 2. OSC1 line is not meant to represent frequency. It is only used to represent time.

- 3. The next rising edge of the internal processor clock following the rising edge of RESET# initiates the reset sequence. to is 1.5toyo minimum.

- initiates the reset sequence. t<sub>RL</sub> is 1.5t<sub>CYC</sub> minimum.

4. The LPRST# pin resets the CPU like RESET#. However, 4064 clock cycles are counted before the reset vector address appears on the internal address bus.

#### FIGURE 8-1: RESET# AND LPRST# TIMING DIAGRAM

# 9.0 POWER-DOWN MODES

SST65P542R offers two modes to reduce system power consumption.

#### 9.1 STOP Mode

To enter the STOP Mode, write 01H to the Power Saving Control Register (PSCR - 0018H). Upon completion of the Write operation to the PSCR, the internal oscillator is turned off, halting all internal processing, including CMT and timer operations.

The microcontroller can be brought out of the STOP Mode by external/Port B interrupts, LPRST# or RESET#.

When external interrupt is asserted (either on IRQ# or Port B pins (when Port B interrupt is enabled)), interrupt will be serviced if mask bit (I bit) is clear, otherwise interrupt will not be serviced. MCU will resume operation to the next instruction byte following the STOP mode enabling Write operation.

The STOP bit will be set to 1 when the device has ben brought out of STOP mode. The I bit will not be affected.

# 9.2 IDLE Mode

To enter IDLE Mode, write 02H to Power Saving Control Register (0018H). The IDLE Mode consumes more power than the STOP Mode. Upon completion of the Write operation to the PSCR, all modules remain active except MCU clock processing is suspended. Any interrupt or reset will cause the MCU to exit IDLE mode.

When an interrupt is asserted, interrupt will be serviced if mask bit (I bit) is clear, otherwise interrupt will not be serviced. MCU will resume operation to the next instruction byte following the IDLE mode enabling Write operation. The IDLE bit will be set to 1 when the device has been brought out of IDLE mode. The I bit will not be affected.

#### 10.0 THE CORE TIMER

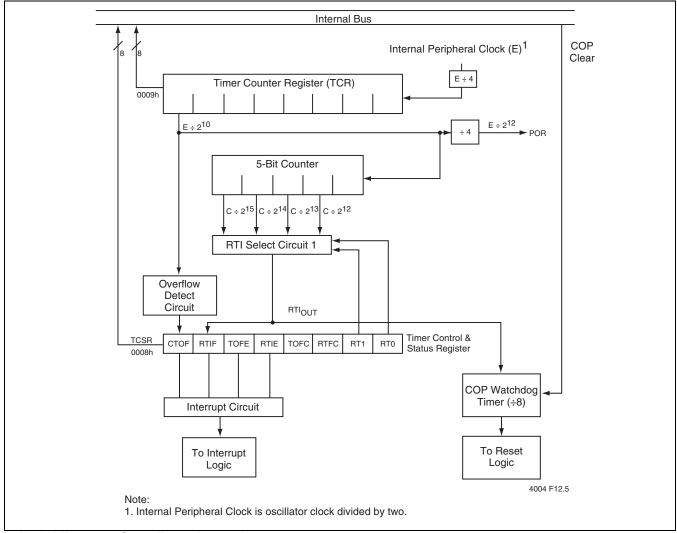

The core timer is a 14-stage, multifunctional ripple counter. Its features include Timer Overflow (TO), Power-On Reset (POR), Real-Time Interrupt (RTI), and COP Watchdog Timer (CWT).

The core timer operates as follows:

- 1. The internal peripheral clock is divided by four, driving an 8-bit ripple counter. At any time, the counter value can be read by accessing the Timer Counter Register (TCR) address 0009H.

- 2. At the last stage of the counter, a timer overflow is implemented. This gives a possible interrupt rate of the internal peripheral clock, E/1024.

- 3. After three more stages, the clock, RTI<sub>OUT</sub>, now E/4096, drives the real-time interrupt circuit (RTI).

- 4. The RTI circuit has three divider stages with a 4:1 selector.

- 5. The output of the RTI circuit is divided by eight. This drives the CWT circuit.

- 6. The Timer Control and Status register at location 0008H contains the RTI rate selector bits and the RTI and CTOF enable bits and flags.

FIGURE 10-1: CORE TIMER BLOCK DIAGRAM

# 10.1 Computer Operating Properly Watchdog Timer Control Register (CWTC)

Writing to CWT Control register (000DH) can enable/disable core timer.